## Syntaktická analýza VHDL

#### Luboš Lorenc, Rudolf Schönecker, Zbyněk Křivka

WFM '07, Hradec nad Moravicí

April 23 - 25

イロト 不得 トイヨト イヨト 三原

1/9

# Outline

- VHDL grammar

- R/R conflicts in VHDL

- Solving of R/R conflicts

- 2 Conditional building of syntactic tree

- Example

- How it works ...

- Results

VHDL grammar R/R conflicts in VHDL Solving of R/R conflicts

- Probably impossible to describe complete VHDL2002 language using context-free grammar.

- Standard is defined using an semantically extended EBNF grammar.

- Particular derivations are permitted using semantic extensions.

- Impossible to remove semantic conditions:

- Rising of a few hundred of R/R conflicts

VHDL grammar R/R conflicts in VHDL Solving of R/R conflicts

## A typical VHDL2002 R/R conflict

- start  $\Rightarrow \cdots \Rightarrow$  type\_mark ';'

- $\texttt{start} \ \Rightarrow \dots \Rightarrow \ \texttt{report\_statement}$

type\_mark

: *type\_*name | *subtype* name

;

report\_statement

```

: REPORT expression ';'

```

;

$\texttt{expression} \ \Rightarrow \ \ldots \Rightarrow \ \texttt{primary}$

primary

- : name

- ;

VHDL grammar R/R conflicts in VHDL Solving of R/R conflicts

## Solving of VHDL2002 R/R conflicts

- It is impossible to left out the semantic information

- There was used two distinct approaches:

- Conditional building of syntactic tree

- It seems to be a hopefull way

- But we are in doubt about realisation

- Creation of an unambiguous grammar

- Meanwhile not succesfull way

- There still remains unsolved R/R conficts

- Probably, there are some other approaches:

- Use of another type of analyser

- Use of huge lookahead

- Analysis based on context-sensitive grammars

- ...

Example How it works... Results

#### The use of auxiliary terminals — example

- start  $\Rightarrow \cdots \Rightarrow$  type\_mark ';'

- $\texttt{start} \Rightarrow \dots \Rightarrow \texttt{report\_statement}$

type\_mark

: name \_TYPE\_ | name \_SUBTYPE\_ ;

report\_statement

```

: REPORT expression ';'

```

;

```

expression \Rightarrow ...\Rightarrow primary

```

primary

- : name

- ;

Example How it works... Results

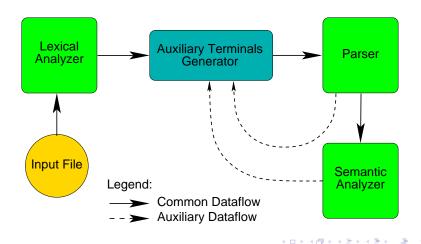

### How it works ....

Example How it works . . . Results

### Conditional building of syntactic tree — results

- All the R/R conflicts solved

- Input file does not contain auxiliary terminals

- Semantic actions of conflicting rules are used to insert auxiliary terminals into input stream

- There is not fully solved needed semantic analysis yet

- Problems may be arisen by an impact of semantics to the syntax (context-sensitive dependencies)

イロト 不得 トイヨト イヨト 三島

# Open problems

- Using auxiliary terminals, there is removed ambiguity from the grammar. But there are two ways how the original VHDL grammar has been created:

- Authors of VHDL2002 created the grammar as a true *unambiguous context-sensitive grammar*:

- Our grammar with auxiliary terminals should be able to simulate the behavior of such a grammar.

- The parser should be able to analyze the whole VHDL2002 language.

- Authors of VHDL2002 created the grammar in some another manner:

- ???

<ロ> (四) (四) (三) (三) (三)