# Scalable Construction of Approximate Multipliers With Formally Guaranteed Worst Case Error

Vojtech Mrazek, Zdenek Vasicek<sup>(D)</sup>, Lukas Sekanina, Honglan Jiang<sup>(D)</sup>, and Jie Han<sup>(D)</sup>

Abstract—Approximate computing exploits the fact that many applications are inherently error resilient. In order to reduce power consumption, approximate circuits such as multipliers have been employed in these applications. However, most current approximate multipliers are based on *ad hoc* circuit structures and, for automated circuit approximation methods, large efficient designs are difficult to find due to the increased search space. Moreover, existing design methods do not typically provide sufficient formal guarantees in terms of error if large approximate multipliers are constructed. To address these challenges, this brief introduces a general and efficient method for constructing large high-quality approximate multipliers with respect to the objectives formulated in terms of the power-delay product and a provable error bound. This is demonstrated by means of a comparative evaluation of approximate 16-bit multipliers constructed by the proposed method and other methods in the literature.

*Index Terms*—Approximate computing circuits and systems, circuit synthesis, circuits, computers and information processing.

#### I. INTRODUCTION

Energy efficiency is a major challenge for current computer systems. Among various techniques, approximate computing exploits the fact that many applications are inherently error resilient and energy requirements can be traded off for the quality of results [1]. Much attention has been paid to the design of approximate arithmetic circuits and, in particular, approximate multipliers, as multiplication is a key operation in many applications.

Approximate implementations of multipliers are based on various design principles (see a recent review in [1]). The major weakness of the *manual circuit design* approach, which is clearly dominating in this area, lies in providing only a few different circuit implementations for a given bit width. Many interesting and useful design points thus remain unexplored. Hence, the automated *search-based design* methods have been developed to provide many approximate designs showing high-quality tradeoffs between key design parameters [2].

We are primarily interested in approximate circuits belonging to the *Pareto set* that contains the so-called *nondominated* solutions. Consider three objectives to be minimized, for example, the powerdelay product (PDP), the worst case error (WCE), and the area. Circuit  $C_1$  *dominates* another circuit  $C_2$  if: 1)  $C_1$  is no worse than  $C_2$  in all objectives and 2)  $C_1$  is strictly better than  $C_2$  in at least one objective.

Search-based methods, however, usually deliver circuits of limited complexity, which especially holds for approximate multipliers. In order to mitigate this issue, an efficient strategy is to compose

Manuscript received March 12, 2018; revised June 4, 2018; accepted July 5, 2018. Date of publication July 31, 2018; date of current version October 23, 2018. This work was supported by the Czech Science Foundation under Grant GA16-17538S. (*Corresponding author: Zdenek Vasicek.*)

V. Mrazek, Z. Vasicek, and L. Sekanina are with the Faculty of Information Technology, IT4Innovations Centre of Excellence, Brno University of Technology, 612 66 Brno, Czech Republic (e-mail: imrazek@fit.vutbr.cz; vasicek@fit.vutbr.cz; sekanina@fit.vutbr.cz).

H. Jiang and J. Han are with the Department of Electrical and Computer Engineering, University of Alberta, Edmonton, AB T6G 2R3, Canada (e-mail: honglan@ualberta.ca; jhan8@ualberta.ca).

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TVLSI.2018.2856362

complex approximate circuits using less complex but high-quality approximate design modules.

For an approximate circuit, another challenge is to find an efficient way to determine the quality (or error) of a design. While small designs can be perfectly evaluated by means of an exhaustive simulation, this problem is not tractable for complex circuits. A circuit simulation using a subset of all input combinations does not, in principle, guarantee an accurate result. Hence, various formal methods capable of determining the "exact" error have been developed in recent years [3]–[5].

To address these challenges, this brief presents a general and efficient method for constructing high-quality nondominated approximate multipliers with the aim to optimize the PDP and design quality. A significant advantage of this method is the ability to analytically provide formal guarantees in terms of the WCE for even complex multipliers. The proposed method exploits the fact that more than two thousands 8-bit approximate multipliers are available and they can directly be employed to construct large approximate multipliers showing various tradeoffs between the design objectives.

## II. EVALUATION OF APPROXIMATE CIRCUITS

Various error metrics have been developed to evaluate the quality of approximate circuits [2], for example, the WCE, sometimes denoted as the maximum error distance, the worst case relative error (WCRE), the average-case error, also known as the mean absolute error (MAE), and the mean relative error (MRE).

The WCE of an *n*-bit approximate multiplier  $\widetilde{M}$  is defined as the maximum difference between the outputs of  $\widetilde{M}$  and a precise multiplier M

$$WCE_{\widetilde{M}} = \max_{\forall a \ b} |\widetilde{M}(a, b) - M(a, b)|$$

(1)

where  $0 \le a, b < 2^n$  and  $M(a, b) = a \times b$ . The WCE can be important in time-critical and dependable systems on the one hand, but also in image and signal processing on the other, where low average error but excessive WCE can produce unacceptable results. The WCRE is defined as

$$WCRE_{\widetilde{M}} = \max_{\forall a, b} \frac{|\widetilde{M}(a, b) - M(a, b)|}{M(a, b)}.$$

(2)

Test vectors are usually applied to estimate the error (e.g.,  $10^7$  input vectors were used to evaluate 16-bit multipliers in [1]). Unfortunately, the accuracy of the simulation-based error evaluation varies with the number and quality of test vectors. This is especially noticeable in the case of WCE, where completely different results may be obtained for a different subset of input vectors.

Current computers only require a few minutes to exactly determine the quality of arithmetic circuits with 16-bit operands. For higher bit widths, a more sophisticated, typically formal, approach has to be involved. The main advantage of the formal approach is that an "exact" error or error bound can be obtained. Checking the WCE can be done using Boolean satisfiability solvers as demonstrated in [6]. Determining the error probability using binary decision diagrams (BDDs) is a relatively straightforward task. For example, Yu and Ciesielski [3] described a method based on BDDs that is

1063-8210 © 2018 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See http://www.ieee.org/publications\_standards/publications/rights/index.html for more information.

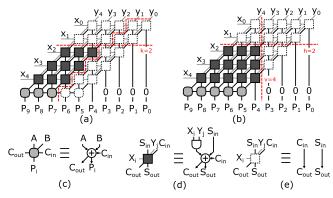

Fig. 1. Hardware architectures of two 5-bit approximate multipliers. (a) TM(5, 2). (b) BAM(5, 4, 2). Omitted cells are shown using dotted cells. Note the inputs of the cells situated in the first row that are not shown are implicitly connected to zero. The following cells are used in the illustration. (c) One-bit full adder. (d) One-bit full adder processing a partial product. (e) Empty (omitted) cell.

able to establish the error probability even for large 64-bit adders. Chandrasekharan *et al.* [4] employed BDDs to determine the worst case arithmetic error. Vasicek *et al.* [5] proposed a method for determining the average-case arithmetic error.

#### **III. APPROXIMATE MULTIPLIERS**

Three stages can be identified in a multiplier: partial product generation, partial product reduction, and final addition. Four main methods are used for the design of approximate multipliers [1]: 1) approximation in generating partial products based on a simpler structure; 2) approximation in the partial product tree by ignoring some partial products (truncation), dividing the partial products into several modules and applying an approximation in the less significant modules, or composing complex approximate multipliers from simple approximate multipliers; 3) using approximate adders, counters, or compressors in the partial product tree to reduce partial products; and 4) using search-based methods to perform approximation on the gate level or in more complex cells. In the sequel, we briefly introduce the state-of-the-art approximate multipliers that provide the best tradeoff between quality and other design parameters such as power, delay, and area.

For *truncated multipliers* (TMs), the key idea is to remove k least significant bits of the input operands. As a result, a smaller (n - k)-bit multiplier is utilized instead of an accurate *n*-bit multiplier. A 5-bit approximate multiplier is implemented as a truncated carry-save adder array in Fig. 1(a). In general, an array multiplier consists of  $n \times n$  cells (i.e., the carry-save adder array) used to reduce partial products, followed by a single *n*-bit merging adder (a ripple carry adder in our example) for the final summation. Due to the truncation, the cells associated with k least significant bits of the first operand (i.e., the circles in the first k rows) and the cells associated with k least significant bits of the second operand (i.e., k rightmost cells of each row) are omitted. As a result, 2k least significant bits of the final product are always zero.

The accuracy of a TM depends on the bit width (n) and the number of truncated bits (k), where  $0 \le k < n$ . The maximum difference between the output of TM(n, k) and a precise multiplier is equal to

WCE<sub>TM(n,k)</sub> =

$$(2^k - 1)(2^{n+1} - 2^k - 1).$$

(3)

In the *broken-array multiplier* (BAM), some of the carry-save adders are removed from an array multiplier [7]. The omitted cells are specified using two parameters: the horizontal break level (h) and vertical break level (v), where  $0 \le h < n$  and  $h \le v < 2n$ . An example of a 5-bit BAM is shown in Fig. 1(b).

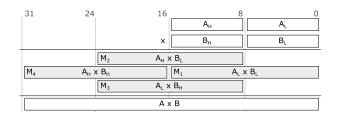

Fig. 2. Construction of a  $2n \times 2n$  multiplier from four  $n \times n$  multipliers denoted as  $M_1$ ,  $M_2$ ,  $M_3$ , and  $M_4$ . The principle is illustrated for n = 8.

In the case that the vertical break level is  $2 \times$  of the horizontal break level (i.e., v = 2h), a structure similar to TM with k = v is obtained. As shown in our example, however, BAM preserves more carry-save adder cells. Since the reduction of carry-save adders can be done in both the directions, the accuracy of BAM(n, h, v) depends on the three parameters. According to [7], the maximum difference is given as

WCE<sub>BAM(n,h,v)</sub> =

$$(2^{n} - 1) \sum_{i=0}^{h-1} 2^{i} + 2^{h} \sum_{i=0}^{v-h-1} (2^{v-h} - 2^{i}).$$

(4)

The maximum relative error is WCRE<sub>BAM</sub> = 1. The MRE significantly increases with increasing v [7].

Recently, a rich library of approximate 8-bit adders and 8-bit multipliers containing hundreds of alternative implementations was introduced [2]. The authors employed a general-purpose approximation method for combinational circuits based on a multiobjective genetic programming. The goal was to simultaneously minimize delay, power consumption, and error to discover a set of approximate circuits along a Pareto front. The basic version of the library contains 471 annotated nondominated 8-bit approximate multipliers that are available for download. Compared with other design methods, a search-based method explores a larger design space, so it is likely to produce approximate multipliers with better hardware characteristics.

Many other approximate multipliers have been proposed. A recent survey of existing implementations can be found in [1]. Unfortunately, the majority of these multipliers were optimized for a single quality parameter only. When multiple quality metrics such as the WCE, MAE, and MRE are considered, they typically show little advantage in the overall performance over a truncated design [1].

#### IV. CONSTRUCTION OF LARGER APPROXIMATE MULTIPLIERS

In order to avoid the time-consuming design loop inherently related with the search-based techniques, we propose to recursively construct complex approximate multipliers, using smaller multipliers.

We employ a divide-and-conquer strategy for synthesizing a 2n-bit multiplier from four n-bit multipliers (see Fig. 2). The operands are divided into four n-bit chunks (each operand has a lower and higher part) that are independently processed using four multipliers whose outputs are reduced using two adders with one n-bit and one 2n-bit operand each.

The key advantage of this method is that each constructed multiplier M has the following properties.

- 1) In the case that all the four *n*-bit multipliers (let us denote them  $M_1-M_4$ ) and adders are accurate, an accurate multiplier is obtained.

- 2) If accurate adders are employed and some of the multipliers are replaced with an approximate multiplier  $\tilde{M}$ , the WCE is equal to

$$WCE_M = 2^{2n}WCE_{M4} + 2^nWCE_{M3} + 2^nWCE_{M2} + WCE_{M1}$$

(5)

TABLE I PROPOSED ARCHITECTURES OF 2*n*-bit APPROXIMATE MULTIPLIERS

| Architecture | $M_1$             | $M_2$             | $M_3$                                               | $M_4$             |  |

|--------------|-------------------|-------------------|-----------------------------------------------------|-------------------|--|

| A1           | $\widetilde{M}$   | accurate          | accurate                                            | accurate          |  |

| A2           | $\widetilde{M}$   | $\widetilde{M}$   | accurate                                            | accurate          |  |

| A3           | $\widetilde{M}$   | $\widetilde{M}$   | $\widetilde{M}$                                     | accurate          |  |

| A4           | $\widetilde{M}$   | $\widetilde{M}$   | $\widetilde{M}$                                     | $\widetilde{M}$   |  |

| A5           | $\widetilde{M}_1$ | $\widetilde{M}_2$ | $\widetilde{M} \ \widetilde{M}_2 \ \widetilde{M}_3$ | $\widetilde{M}_3$ |  |

| A6           | $\widetilde{M}_1$ | $\widetilde{M}_2$ | $\widetilde{M}_3$                                   | $\widetilde{M}_4$ |  |

\* Note that  $\widetilde{M}_i$  may represent approximate or accurate multiplier.

where  $WCE_{M_i} = WCE_{\widetilde{M}}$  iff  $M_i$  is replaced with M and  $WCE_{M_i} = 0$  otherwise.

3) If accurate adders are employed and some of the multipliers are replaced with different approximate multipliers, (5) gives us the upper bound since the approximate multipliers can have dependent inputs.

Clearly, the exact value of WCE<sub> $\tilde{M}$ </sub> can easily be obtained for a reasonable *n* (in our case n = 8) using exhaustive simulation. The question is, how to efficiently determine which multiplier  $M_i$  should be replaced with an approximate multiplier and what approximate multipliers should be used to obtain the best tradeoffs without compiling and synthesizing all the possible design points. In general,  $(n_a + n_e)^4$  possible solutions exist provided that  $n_a$  denotes the number of nondominated approximate *n*-bit multipliers and  $n_e$  is the number of exact *n*-bit multipliers. As more than 2200 different nondominated 8-bit multipliers are available at the extended version of EvoApprox8 library and more than 60 different implementations can be obtained using the approaches proposed in the literature, it is practically infeasible to synthesize all possible implementations (more than 1.4 × 10<sup>11</sup> potential solutions exist).

Hence, we propose the following two strategies. In the *first* strategy, a single approximate multiplier  $\tilde{M}$  is chosen and  $M_1-M_4$  are successively replaced with  $\tilde{M}$  (see A1–A4 in Table I). The advantage of this approach is that it produces a relatively small number of implementations that can easily be synthesized and evaluated. Due to its simplicity, a similar scenario (i.e., some submodules are replaced with a single approximate circuit) is typically employed in quality configurable multipliers such as approximate Wallace tree multiplier [8] or lpAClib [9].

Equation (5) suggests that much better results could be potentially obtained when up to four different approximate 8-bit multipliers are utilized in the 16-bit multiplier. Intuitively,  $M_4$  should produce the lowest error since it has the largest impact on the quality of the obtained multiplier. In order to reduce a huge number of design alternatives that have to be synthesized, the *second strategy* is proposed. In its first phase, we filter out all approximate 16-bit multipliers that are dominated by some other multipliers. This can be done relatively quickly and without using a professional design tool if the precomputed circuit parameters [WCE calculated according to (5), power consumption calculated as the sum of power consumption of all 8-bit multipliers' areas] are used instead of "exact" values. In the second phase, only the circuits identified in the first phase are synthesized and thoroughly evaluated.

In the multiplier denoted as A6 in Table I, four different approximate multiplier modules are utilized. For example, if there are 258 different 8-bit approximate multipliers, there exist  $258^4 = 4,430,766,096$  different 16-bit approximate multipliers using the A6 architecture. However, most of the 16-bit approxi-

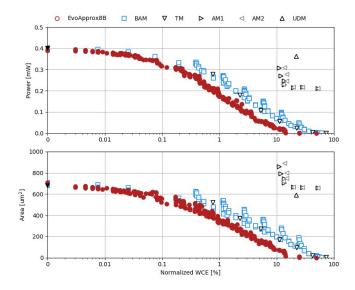

Fig. 3. Measurements of various 8-bit multipliers synthesized using 45nm technology. The multipliers forming a Pareto set considering power, area, and WCE are highlighted using filled markers. Normalized WCE (NWCE) is calculated as NWCE = WCE/ $2^{2n}$ , where *n* is equal to 8. Measurements of five different exact multipliers are provided as the points at WCE = 0.

mate multipliers are dominated by others and can be filtered out. As a result, only 6753 multipliers remain for further evaluation. To significantly reduce the number of 16-bit multipliers that have to be investigated in the first phase, we also consider the architecture A5 that contains only three different approximate 8-bit multipliers (see Table I).

#### V. EXPERIMENTS AND SIMULATION RESULTS

Although the proposed method is applicable to an arbitrary bit width, the construction of 16-bit multipliers is investigated because the 16-bit multipliers can be evaluated by simulation that enables to thoroughly evaluate the proposed method and compare the obtained circuits with existing designs.

#### A. Evaluation of 8-bit Approximate Multipliers

First, we implemented all relevant 8-bit multipliers in Verilog Hardware Description Language (VHDL) and synthesized them together with multipliers from the EvoApprox8b library. Synopsys design compiler with 45-nm PDK was employed for synthesis. Each VHDL model was converted to an equivalent C code that was utilized for quality analysis. Exact values of WCE, WCRE, error rate, MAE, and MRE were determined by using all 2<sup>16</sup> input vectors. In this phase, more than 2210 implementations were synthesized and analyzed. The obtained results are shown in Fig. 3. The naming of the multipliers corresponds with [1]. Only nondominated solutions are shown for each architecture for clarity. The results show the advantages of TM, BAM, and EvoApprox8b over the other designs when WCE and circuit area or power consumption are considered. Considering WCE, MAE, and MRE, EvoApprox8b designs outperform the other ones. In addition to that, they fill the missing spaces that are unreachable by truncation. Fig. 3 also contains the measurements of an accurate multiplier implemented using the star operator in VHDL (see the triangle at WCE = 0). Interestingly, many approximate multipliers (some instances of AM1, AM2, and underdesigned multiplier) require a larger area compared to the accurate multipliers.

#### B. Synthesis of 16-bit Approximate Multipliers

From the previous results, 258 nondominating design points were identified (by considering WCE, PDP, and area only) and employed

NUMBER OF NONDOMINATED MULTIPLIERS  $(n_{dom})$  Identified in the First/Second Phase and the Corresponding Runtime (Filtration  $t_{filt}$ , Synthesis  $t_{syn}$ , and Analysis  $t_{ev}$ ) in Minutes

| Arch. | First phase (filtration) |           |            | Second phase |           |          | Total   |

|-------|--------------------------|-----------|------------|--------------|-----------|----------|---------|

|       | $n_{total}$              | $n_{dom}$ | $t_{filt}$ | $n_{dom}$    | $t_{syn}$ | $t_{ev}$ | runtime |

| A1    | 258                      | 258       | -          | 192          | 10        | 42       | 52      |

| A2    | 258                      | 258       | -          | 158          | 10        | 42       | 52      |

| A3    | 258                      | 258       | -          | 158          | 10        | 42       | 52      |

| A4    | 258                      | 258       | -          | 142          | 10        | 42       | 52      |

| A5    | $1.7\cdot 10^7$          | 4,449     | 2          | 810          | 180       | 720      | 902     |

| A6    | $4.4\cdot 10^9$          | 6,753     | 469        | 1,257        | 273       | 1,093    | 1,846   |

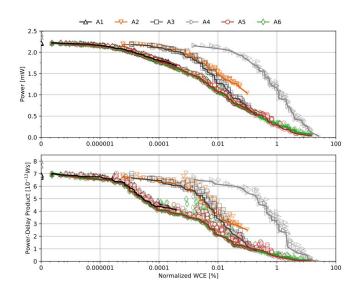

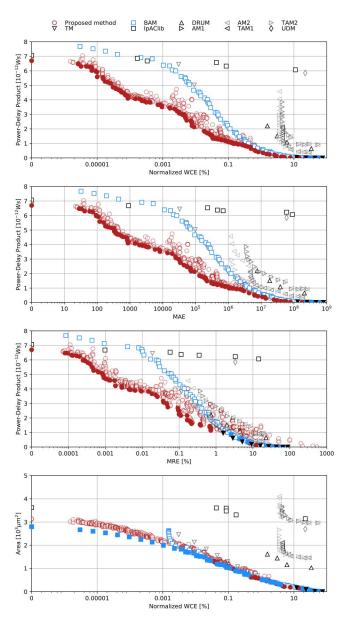

Fig. 4. Measurements of 16-bit approximate multipliers consisting of four 8-bit multipliers using the proposed approaches A1–A6. The implementations lying on the Pareto set, determined for each method and each plot separately, are shown using a line.

as  $\tilde{M}$  or  $\tilde{M}_i$ . This yields  $4 \times 258 = 1032$  different implementations of A1–A4. In addition to that, 4449 different implementations of A5 and 6753 different implementations of A6 were produced in the first phase. Then, the 16-bit implementations were synthesized using synopsys design compiler and analyzed using a simulator with  $2^{32}$  input vectors to obtain exact values of WCE, WCRE, MAE, and MRE. The accurate carry lookahead adder was employed in all designs. The runtimes for filtration, synthesis, and analysis are given in Table II. After synthesis and analysis, 192 (respectively, 158, 158, 142, 810, and 1257) nondominated solutions<sup>1</sup> were identified for A1 (respectively, A2, A3, A4, A5, and A6). Measurements of the nondominated designs are shown in Fig. 4. For illustration, we also included dominated solutions.

The results validate our assumption regarding the quality of approximate multipliers using the proposed architecture A6 compared to the basic construction mechanisms A1–A4. Interestingly, there is no significant difference between the multipliers using A5 and A6. Considering this fact, A5 is a very efficient architecture for constructing multipliers of higher bit widths. Compared to A6, it requires approximately  $2\times$  smaller computational power as shown in Table II. Although only exact WCE is plotted due to the limited space, this observation is valid for MAE and MRE too (see Fig. 5). The remaining results can be found at our website.<sup>2</sup>

Fig. 5. Comparison of the proposed 16-bit approximate multipliers (using the A5 architecture) with multipliers from the literature across various quality indicators. The multipliers on a Pareto set, determined for each plot separately, are highlighted using filled markers. Parameters of exact multipliers are provided as the points at WCE = 0.

For some instances, (5) provides the upper bound and the exact WCE may be lower than the estimated one. Although this cannot have a negative impact on a real application, knowledge of the exact and estimated WCE offers an opportunity for a more detailed analysis. Considering 6753 different implementations of A6, the nonzero difference occurs in 85%. The mean (respectively, median and maximum) difference is 2.8% (respectively, 2.2% and 16.6%). Difference greater than 5% occurs in 13%.

# C. Comparison With the State-of-the-Art Approaches

The detailed comparison of the proposed method with the stateof-the-art designs is shown in Fig. 5. For evaluation with the typical error metrics, we reimplemented the approximate multipliers that are believed to provide the best results according to the latest review [1]. In total, 244 different 16-bit designs were created, synthesized, and evaluated. For configurable architectures (AM, BAM, truncated

<sup>&</sup>lt;sup>1</sup>Power, area, delay, WCE, and MRE were considered.

<sup>&</sup>lt;sup>2</sup>http://www.fit.vutbr.cz/research/groups/ehw/approxlib/

array multiplier (TAM), approximate compressor-based multiplier, and lpAClib), all meaningful configurations were considered. The error metrics are evaluated accurately using all test vectors for all considered designs.

The results are mostly consistent with the review [1], although some multipliers exhibit lower quality (see TAM1). The differences are probably caused by the fact that a different technology node generation is considered with a different cell library. We also determine the errors exactly, whereas only a small fraction (0.2%) of all possible input combinations is employed in the review to assess the quality of the approximate multipliers. While the quality of particular designs varies depending on the chosen error criteria, the truncated multipliers (TM and BAM) exhibit stable performance and achieve excellent design tradeoffs.

The multipliers constructed using the proposed method provide the best tradeoffs except for the area versus WCE result, whereas BAMs occupy smaller area. Despite the fact that only the WCE, power, and area were considered to obtain nondominated designs, the obtained multipliers perform well even under MAE and MRE. In fact, it is shown that MAE strongly correlates with WCE.

In order to construct a database of 810 annotated 16-bit multipliers, 15 h (including quality evaluation taking more than 80% of the total runtime) were required on an eight-core Intel Xeon CPU at 2.4 GHz.

### VI. CONCLUSION

In this brief, a scalable recursive method for the construction of large approximate multipliers with guaranteed WCE was proposed. We demonstrated how to relatively quickly construct a high-quality Pareto set of nondominated 2n-bit approximate multipliers provided that we have a reasonable database of *n*-bit approximate multipliers.

We show that it is sufficient to construct a 2n-bit multiplier using three different n-bit multipliers (in the architecture A5) without

sacrificing much quality of the obtained 2*n*-bit multipliers. This method enables to reduce the design time to nearly one half of the A6 architecture, in which four different 8-bit multipliers are selected. The constructed designs show WCEs limited by a maximum error bound that can be analytically obtained due to the proposed design approach.

#### REFERENCES

- H. Jiang, C. Liu, L. Liu, F. Lombardi, and J. Han, "A review, classification, and comparative evaluation of approximate arithmetic circuits," *J. Emerg. Technol. Comput. Syst.*, vol. 13, no. 4, 2017, Art. no. 60.

- [2] V. Mrazek, R. Hrbacek, Z. Vasicek, and L. Sekanina, "EvoApproxSb: Library of approximate adders and multipliers for circuit design and benchmarking of approximation methods," in *Proc. DATE*, Mar. 2017, pp. 258–261.

- [3] C. Yu and M. Ciesielski, "Analyzing imprecise adders using BDDs—A case study," in *Proc. ISVLSI*, Jul. 2016, pp. 152–157.

- [4] A. Chandrasekharan, M. Soeken, D. Große, and R. Drechsler, "Approximation-aware rewriting of AIGs for error tolerant applications," in *Proc. ICCAD*, Nov. 2016, pp. 1–8.

- [5] Z. Vasicek, V. Mrazek, and L. S. Brno, "Towards low power approximate DCT architecture for HEVC standard," in *Proc. DATE*, Mar. 2017, pp. 1576–1581.

- [6] R. Venkatesan, A. Agarwal, K. Roy, and A. Raghunathan, "MACACO: Modeling and analysis of circuits for approximate computing," in *Proc. ICCAD*, Nov. 2011, pp. 667–673.

- [7] H. R. Mahdiani, A. Ahmadi, S. M. Fakhraie, and C. Lucas, "Bio-inspired imprecise computational blocks for efficient VLSI implementation of soft-computing applications," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 57, no. 4, pp. 850–862, Apr. 2010.

- [8] K. Bhardwaj, P. S. Mane, and J. Henkel, "Power- and area-efficient approximate wallace tree multiplier for error-resilient systems," in *Proc. 15th Int. Symp. Quality Electron. Design (ISQED)*, Mar. 2014, pp. 263–269.

- [9] M. Shafique, W. Ahmad, R. Hafiz, and J. Henkel, "A low latency generic accuracy configurable adder," in *Proc. DAC*, Jun. 2015, pp. 1–6.